Revision history

220823

- Xilinx Primitive 추가

what''s initial value of register without power-on reset?

support.xilinx.com

예문

reg [3:0] cnt;always @ (posedge clk or posedge rst)

if( rst ) begin

cnt<=3;

end

else begin

cnt<=cnt\+1;

end

FPGA configureation 후의 register의 초기값은 FD*E cell의 값에 의해 결정됨

FD*E cell값 설정 방법:

1.

(verilog) reg <register_name> = 1'b0 또는 1'b1

(VHDL) signal <signal_name> : std_logic := '0' 또는 '1'

2. 합성 후에 Tcl 명령어로 INIT property값을 입력: set_property INIT 1'b0 [get_cells reg_name]

3. FD*E cell의 초기값이 입력되지 않았다면 FD*E cell의 reset 초기값으로 결정됨

FDRE, FDCE의 rest 초기값: 0

FDSE, FDPE의 rest 초기값: 1

예) 아래 코드는 FDSE초기값이 1로 설정됨(when -control_set_opt_threshold set to 0)

reg dout;

always @ (posedge clk)

if(rst)

dout <= 1'b1;

else

dout <= din;

Note: When there is initial value specified with the signal declaration but different from the reset value, the former takes priority over the latter.

4. FD*Ecell의 초기값이 없고 reset을 사용하지 않았다면 초기값은 0

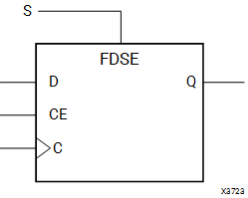

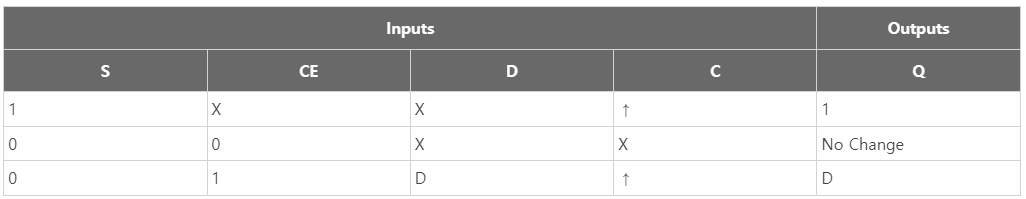

FDSE란?

URL: https://docs.xilinx.com/r/2021.2-English/ug953-vivado-7series-libraries/FDSE

Primitive: D Flip-Flop with Clock Enable and Synchronous Set

FDSE is a single D-type flip-flop with data (D), clock enable (CE), and synchronous set (S) inputs and data output (Q).

220823 추가

그 외에도

FDCE Primitive: D Flip-Flop with Clock Enable and Asynchronous Clear

FDPE Primitive: D Flip-Flop with Clock Enable and Asynchronous Preset

FDRE Primitive: D Flip-Flop with Clock Enable and Synchronous Reset

FDSE Primitive: D Flip-Flop with Clock Enable and Synchronous Set

등이 있다.

'FPGA > 개발' 카테고리의 다른 글

| [Vivado 2020.2] Block Design 변경 시 시뮬레이션 업데이트 방법 (0) | 2022.06.14 |

|---|---|

| [UltraScale Architecture GTH Transceiver] RX Byte and Word Alignment (0) | 2022.05.30 |

| [Simulation] AXI read write tasks (0) | 2022.04.05 |

| [Xilinx] Native Block Memory Generator (0) | 2022.03.14 |

| [Vivado 2020.2] Block design내 hierarchy 시뮬레이션 방법 (0) | 2022.03.07 |