Top block design내 hierarchial submodule인 clocking_system 시뮬레이션 방법

1. Generate the Output Products 실행

2. Testbench에서 clocking_system을 instantiate

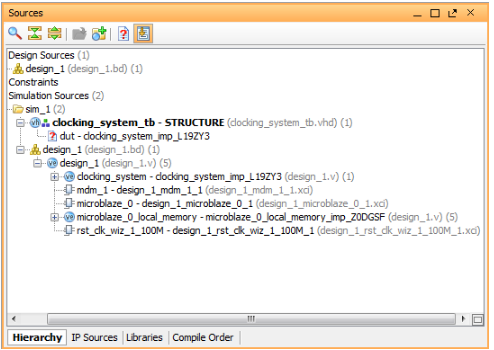

- source탭에서 design_1 → design_1 → clocking_system - clocking_system_imp_L19ZY3이 보이는데 이것이 instantiate을 할 때 쓰이는 이름이고 the unique component/module name 이라고 한다.

- VHDL instatiate

- Verilog instantiate

clocking_system_imp_L19ZY3 dut (

.clk (CLK),

.out_clk (out_clk)

);

3. Intatiate를 하면 아래처럼 파일에 ?가 나타나는데 시뮬레이션에는 지장이 없다. (정상)

4. 마지막으로 시뮬레이션 하기 전에 "set the Hierarchy Update to Automatic Updte"가 기본으로 설정이 되어있는데 이것을 "Manual Compile Order"로 변경한다.

이것은 Vivado 툴 컴파일러가 필요한 소스만 컴파일 하는것이 아니라 모든 소스들을 컴파일 하도록 만든다.

URL: https://support.xilinx.com/s/article/60703?language=en_US

'FPGA > 개발' 카테고리의 다른 글

| [Simulation] AXI read write tasks (0) | 2022.04.05 |

|---|---|

| [Xilinx] Native Block Memory Generator (0) | 2022.03.14 |

| [Vivado 2020.2] Subblock design (Hierarchy)를 다른 Vivado 프로젝트로 복사 방법 (0) | 2022.02.24 |

| Vitis 사용법 (0) | 2022.02.22 |

| Processor SystemReset Module v5.0 (0) | 2022.02.15 |